### UNIVERSITY OF CALIFORNIA SANTA CRUZ

# A STUDY OF FRAMEWORKS FOR COLLECTIVELY ACHIEVING THE PRODUCTIVITY, PORTABILITY, AND ADOPTABILITY GOALS OF PARALLEL SOFTWARE

A dissertation submitted in partial satisfaction of the requirements for the degree of

DOCTOR OF PHILOSOPHY

in

COMPUTER ENGINEERING

by

Sean Halle

June 2011

| The Dissertation of Sean Halle is approved: |

|---------------------------------------------|

| Professor Jose Renau, Chair                 |

| Professor Cormac Flanagan                   |

| Professor Albert Cohen                      |

Tyrus Miller

Vice Provost and Dean of Graduate Studies

# Contents

| Li           | st of            | Figures                                                       | iv |

|--------------|------------------|---------------------------------------------------------------|----|

| Li           | $\mathbf{st}$ of | Tables                                                        | v  |

| $\mathbf{A}$ | bstra            | act                                                           | vi |

| D            | edica            | ation                                                         | х  |

| A            | ckno             | wledgments                                                    | xi |

| 1            | Mo               | tivation and Overview                                         | 1  |

| Ι            | $\mathbf{M}$     | odel of the Problem                                           | 6  |

|              |                  | 1.0.1 Dealing with Imprecision and Subjectivity               | 7  |

| <b>2</b>     | Soft             | tware Segments                                                | 9  |

|              | 2.1              | Infrastructure Surrounding Applications                       | 9  |

|              | 2.2              | The Software Segments                                         | 11 |

|              |                  | 2.2.1 Listing of the Segments                                 | 13 |

|              |                  | 2.2.2 Conclusions about the Segments                          | 21 |

|              | 2.3              | Focus on Distribution and the Implications for BLISS          | 21 |

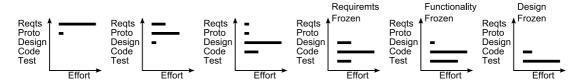

|              | 2.4              | Model of the Development Process                              | 24 |

|              |                  | 2.4.1 Overview of Development Workflow                        | 24 |

|              |                  | 2.4.2 Details of the Development Iterations                   | 26 |

|              | 2.5              | Applying Development-Process Knowledge to Language Design     | 29 |

| 3            | Ind              | ividual Human Factors                                         | 31 |

|              | 3.1              | How People Handle Parallelism in the Real World               | 32 |

|              | 3.2              | Personal Preferences in Development                           | 34 |

|              |                  | 3.2.1 No One-size-fits-all Development                        | 35 |

|              |                  | 3.2.2 Variation in Languages:                                 | 35 |

|              |                  | 3.2.3 Conclusion, Framework Best when Supports Many Languages | 36 |

|              | 3.3              | Human Aspects of Productivity                                 | 36 |

|              |                  | 3.3.1 Variation Among People                                  | 37 |

|              |                  | 3.3.2 Match Language to Thought Patterns                      | 38 |

|   |     | 3.3.3         | Conclusions Based on the Complexity of Productivity                | 40              |

|---|-----|---------------|--------------------------------------------------------------------|-----------------|

| 4 | Mod | del of        | Adoption                                                           | 43              |

| _ | 4.1 |               | erson Projects                                                     | 45              |

|   | 4.2 |               | m Sized Projects                                                   | 46              |

|   | 4.3 |               | Projects                                                           | 47              |

| 5 | Ovo | rviou         | of Portability                                                     | 50              |

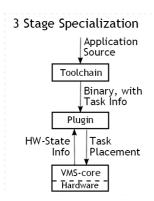

| 9 | Ove | 5.0.1         | Specialization                                                     | 50              |

|   |     | 5.0.1 $5.0.2$ | Why a New Basic Model of Computation?                              | 51              |

|   | 5.1 |               | iew of the Basic Computation Model                                 | 52              |

|   | 5.1 |               | iew of Parallelism Model                                           | $\frac{52}{52}$ |

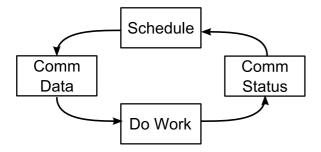

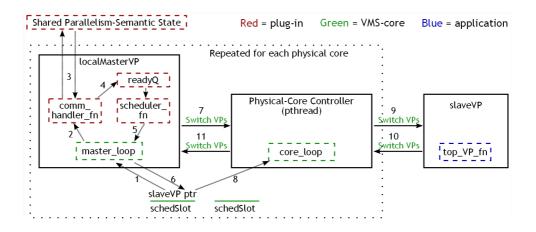

|   | 0.2 | 5.2.1         | The Scheduling Loop                                                | 53              |

|   |     | 5.2.1         | Conclusions Drawn from the Holistic Model                          | 53              |

|   |     | 5.2.3         | Main Result of Holistic Model                                      | 55              |

|   | 5.3 | 00            | iew of Specialization                                              | 56              |

|   | 0.0 | 0 10111       |                                                                    |                 |

| 6 | A B |               | omputation Model Featuring Scheduling                              | <b>57</b>       |

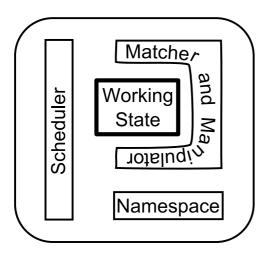

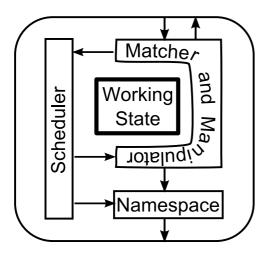

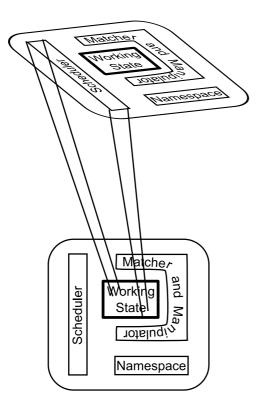

|   | 6.1 |               | tion of Processor                                                  | 58              |

|   |     | 6.1.1         | Memory Processors                                                  | 63              |

|   |     | 6.1.2         | Applying the Model, Take One                                       | 64              |

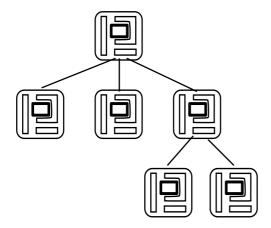

|   |     | 6.1.3         | Hierarchy of Processors Contained Inside Others                    | 66              |

|   | 6.2 |               | of a Processor, Time, and Animation                                | 67              |

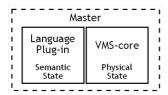

|   |     | 6.2.1         | Kinds of State in a Processor                                      | 67              |

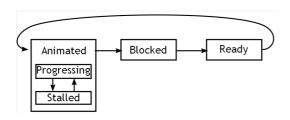

|   |     | 6.2.2         | Animation                                                          | 68              |

|   |     | 6.2.3         | Animation vs Namespace                                             | 69              |

|   |     | 6.2.4         | More on the Nature of Time in the Model                            | 70              |

|   |     | 6.2.5         | Data vs Pattern                                                    | 72              |

|   | 6.3 | -             | alent Circuit and Shape-Control Data vs Flow-Through Data          | 75              |

|   |     | 6.3.1         | Equivalent Circuit:                                                | 75              |

|   |     | 6.3.2         | Shape-Control Data vs Flow-Through Data                            | 75              |

|   |     | 6.3.3         | The Amount of Work Done by a Processor                             | 76              |

|   | 0.4 | 6.3.4         | Grouping Code by its Use of Data                                   | 78              |

|   | 6.4 |               | tion Models                                                        | 79              |

|   |     | 6.4.1         | Applying the basic model to Von Neumann processors                 | 80              |

|   |     | 6.4.2         | Imprecision is Intentional                                         | 82              |

|   |     | 6.4.3         | Scheduling is the Difference In Sequential vs Parallel Programming | 84              |

| 7 | Hol |               | Iodel of Parallel Computation                                      | 87              |

|   | 7.1 | 0             | iew of the Model                                                   | 88              |

|   |     | 7.1.1         | Holistic Scheduler is in the Animator                              | 88              |

|   |     | 7.1.2         | What the Model Shows                                               | 88              |

|   |     | 7.1.3         | How Hardware Affects Performance                                   | 90              |

|   |     | 7.1.4         | Simplifications of the Model                                       | 90              |

|   |     | 7.1.5         | What Want from the Model                                           | 91              |

|   | 7.2 |               | is Parallelism?                                                    | 92              |

|   |     | 7.2.1         | Hardware View of Parallelism                                       | 92              |

|   |     | 7.2.2         | Programmer View of parallelism                                     | 94              |

|   |     | 7.2.3         | Toolchain View of Parallelism                                      | 95              |

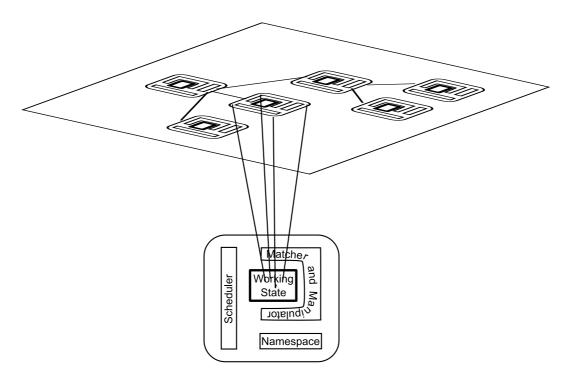

|   | 7.3         | The Holistic Model of Parallel Computation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 95                                                                                                    |

|---|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

|   |             | 7.3.1 Inputs to the Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                       |

|   |             | 7.3.2 Overview of the Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 97                                                                                                    |

|   |             | 7.3.3 Interactions Among Elements in the Scheduling Loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 100                                                                                                   |

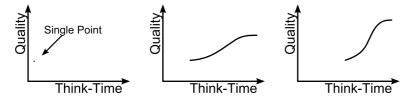

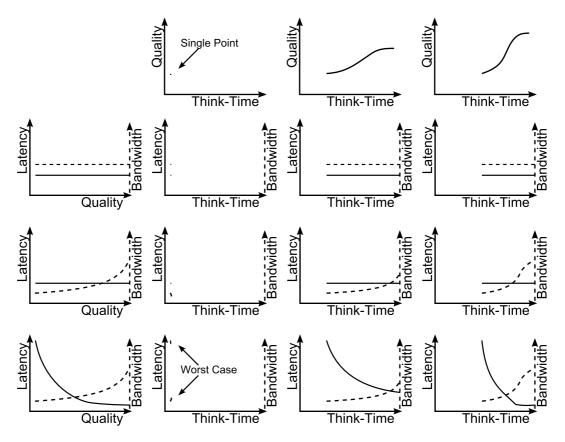

|   | 7.4         | Thought Experiments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 101                                                                                                   |

|   |             | 7.4.1 Thought Experiments on Effect of Scheduler Abilities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 102                                                                                                   |

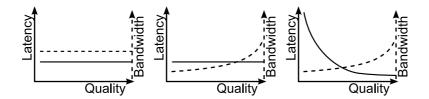

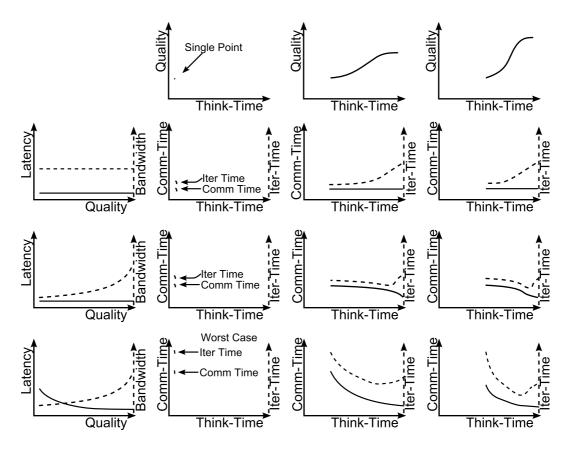

|   |             | 7.4.2 Combining Communication Curves with Quality Curves                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 104                                                                                                   |

|   |             | 7.4.3 Iteration Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                       |

|   | 7.5         | Total Running Time vs Iteration Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 108                                                                                                   |

|   |             | 7.5.1 Task dependency graph constraints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                       |

|   |             | 7.5.2 Hardware resource limitations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 112                                                                                                   |

|   |             | 7.5.3 Communication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                       |

|   |             | 7.5.4 Effect of choice of task boundaries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 113                                                                                                   |

|   |             | 7.5.5 Virtualizing Resources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                       |

|   |             | 7.5.6 Conclusions from Thought Experiments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                       |

|   | 7.6         | Relation Between Scheduler, Application, and Hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                       |

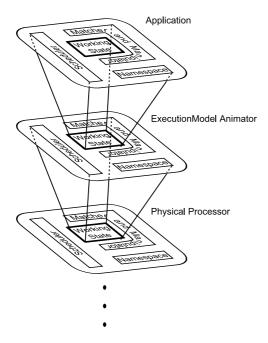

|   |             | 7.6.1 Animator Hierarchy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                       |

|   |             | 7.6.2 The Scheduler Abilities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 118                                                                                                   |

|   |             | 7.6.3 Task Characteristics Enable or Disable Scheduler Abilities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 122                                                                                                   |

|   |             | 7.6.4 Hardware Characteristics Enable or Disable Scheduler Abilities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 123                                                                                                   |

|   |             | 7.6.5 Extract Task and Hardware Characteristics for the Animator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                       |

|   |             | 7.6.6 Hardware Interactions with Software Affect Scheduler Decisions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                       |

|   |             | 7.6.7 Choose Scheduler by Both Task and HW Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 125                                                                                                   |

| 8 | Spe         | ecialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 128                                                                                                   |

| O | 8.1         | What is specialization?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                       |

|   | 0.1         | 8.1.1 The Four Things at the Heart of Specialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                       |

|   | 8.2         | When is Specialization Performed?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                       |

|   | ٠. <b>_</b> | 8.2.1 Choosing When in Application Lifetime to Specialize                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                       |

|   |             | 8.2.2 Examples of Specialization at Various Lifetime Points                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -00                                                                                                   |

|   | 8.3         | c.=.= Entering of Specialization at various Encounter of the control of the contr | 133                                                                                                   |

|   | 0.0         | Where is Specialization Performed?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                       |

|   | 8 4         | Where is Specialization Performed?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 134                                                                                                   |